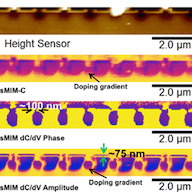

Insulated Gate Bipolar Transistor (IGBT)

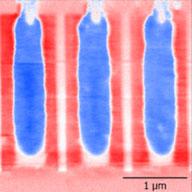

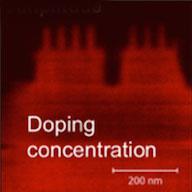

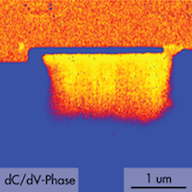

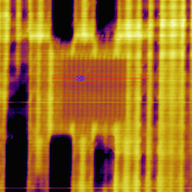

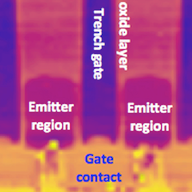

Image is the sMIM dC/dV Amplitude signal of a vertical Insulated gate bipolar transitor (IGBT). The sampe was imaged using a 1V AC bias applied between tip and sample. The dC/dV amplitude is sensitive to the doping concentration of the cross-sectioned devices. The image shown has a very high level of detail for the emmiter, gate metals, and even at the high doped region of the gate region with oxide interface.